Microcontroller-based Switch Mode Power Supplies need to be both real-time and deterministic, while also taking advantage of the flexibility offered by programmable microcontrollers. The firmware for these power supplies handles various tasks, some of which must be deterministic, while others, being less critical, do not require deterministic execution. This design approach is evident in the use of interrupts and the repetition of tasks at different frequencies. These aspects will be explored in detail in the Firmware Structure and Implementation section later.

The Firmware for PSFB DCDC Converter has the following components

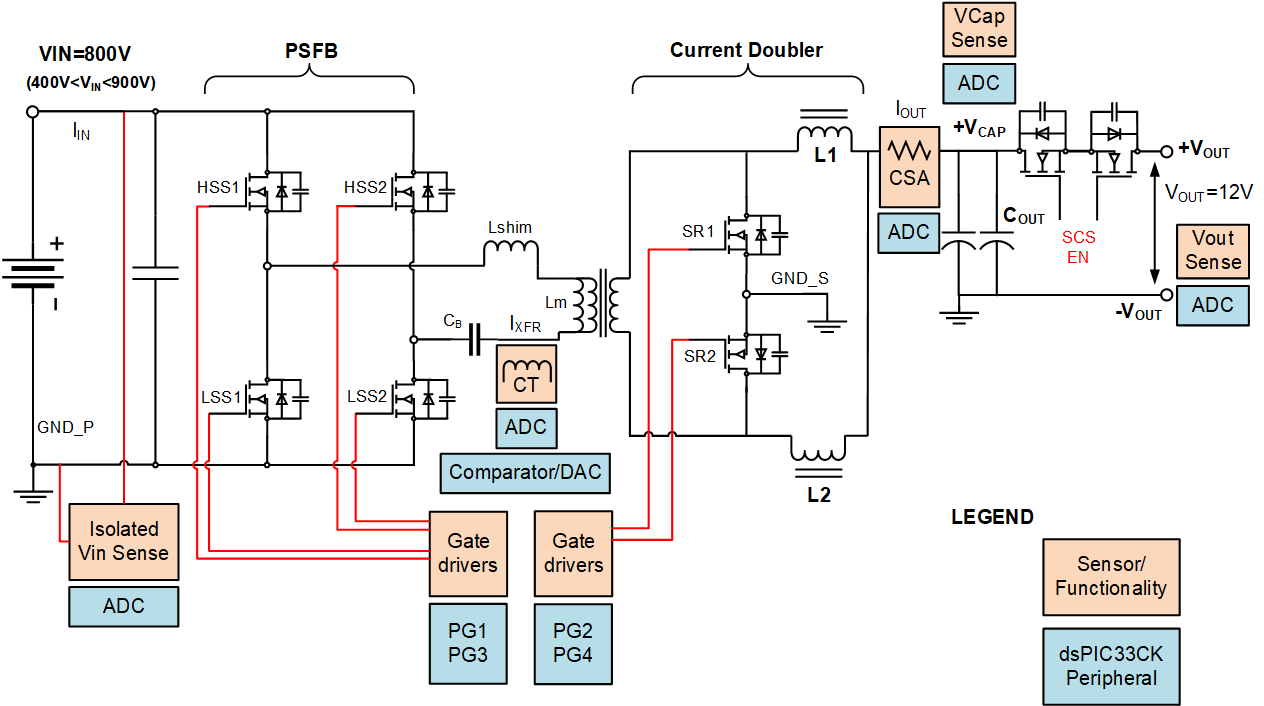

When designing a power converter, it's important to monitor both the input and output voltages and currents. This is done by scaling the voltages to levels that the microcontroller's ADC sense lines can handle. The primary side current is measured with a current transformer, while the output current is detected using a shunt amplifier. Both of these current measurements are then converted into voltage signals that the analog sense lines can process.

The dsPIC33CK256MP506 devices have a high-speed, 12-bit Analog-to-Digital Converter (ADC) that features a low conversion latency, high resolution and oversampling capabilities to improve performance in AC/DC, DC/DC power converters. The devices implement the ADC with three SAR cores, two dedicated and one shared. Two of these cores are faster dedicated cores which are dedicated to specific channels and are used to sample the input and output currents. The other core, which is a shared core supporting a higher number of channels, is used to sample the input and output voltages.

Following table lists all the analog channels of the PSFB converter

| S.no | Net name | MCU details | Description | Sampling Trigger | Sampling Rate |

|---|---|---|---|---|---|

| 1 | FB_P_CT_FILT | Dedicated Core 0 Conversion Time: 328ns | Primary Current. Sensed through a CT. | Sampled at half of the Duty Cycle. | Sampled Cycle by Cycle, 100kHz |

| 2 | I_SEC_AVG_FILT | Dedicated Core 1 Conversion Time: 328ns | Output Current. Sensed through Shunt. | Sampled at half of the Duty Cycle. | Sampled Cycle by Cycle, 100kHz |

| 3 | FB_VOUT | Shared Core Channel 2 Conversion Time: 470ns | Output Voltage Shared Core, Channel 2 | Sampled at half of the Duty Cycle | Sampled Cycle by Cycle, 100kHz |

| 4 | VIN_INT_AN | Shared Core Channel 10 Conversion Time: 670ns (value available after 670ns after triggering) | Input Voltage | Software Trigger | Sampled Cycle by Cycle, 100kHz |

| 5 | FB_VCAP | Shared Core Channel 9 Conversion Time: 470ns (value available after 470ns after triggering) | Output Capacitor Voltage | Software Trigger | Sampled Cycle by Cycle, 100khz |

| 5 | FP_TEMP | Shared Core Channel 14 Conversion Time: 900ns (value available after 900ns after triggering) | Temperature Sensor | Software Trigger | Sampled Cycle by Cycle, 100khz |

| 6 | FB_5V | Shared Core Channel 19 Conversion Time: 1400ns (value available after 1388ns after triggering) | 5 Volt Rail | Software Trigger | Sampled Cycle by Cycle, 100khz |

Input and Output Current sensors both have offsets of about 500mV. These are measured before power transfer.

In phase shifted design, the power transfer happens by the phase-shift between the fixed and phase shifted legs of the bridge. Due to this phase shift a bipolar voltage appears at the primary of the transformer.

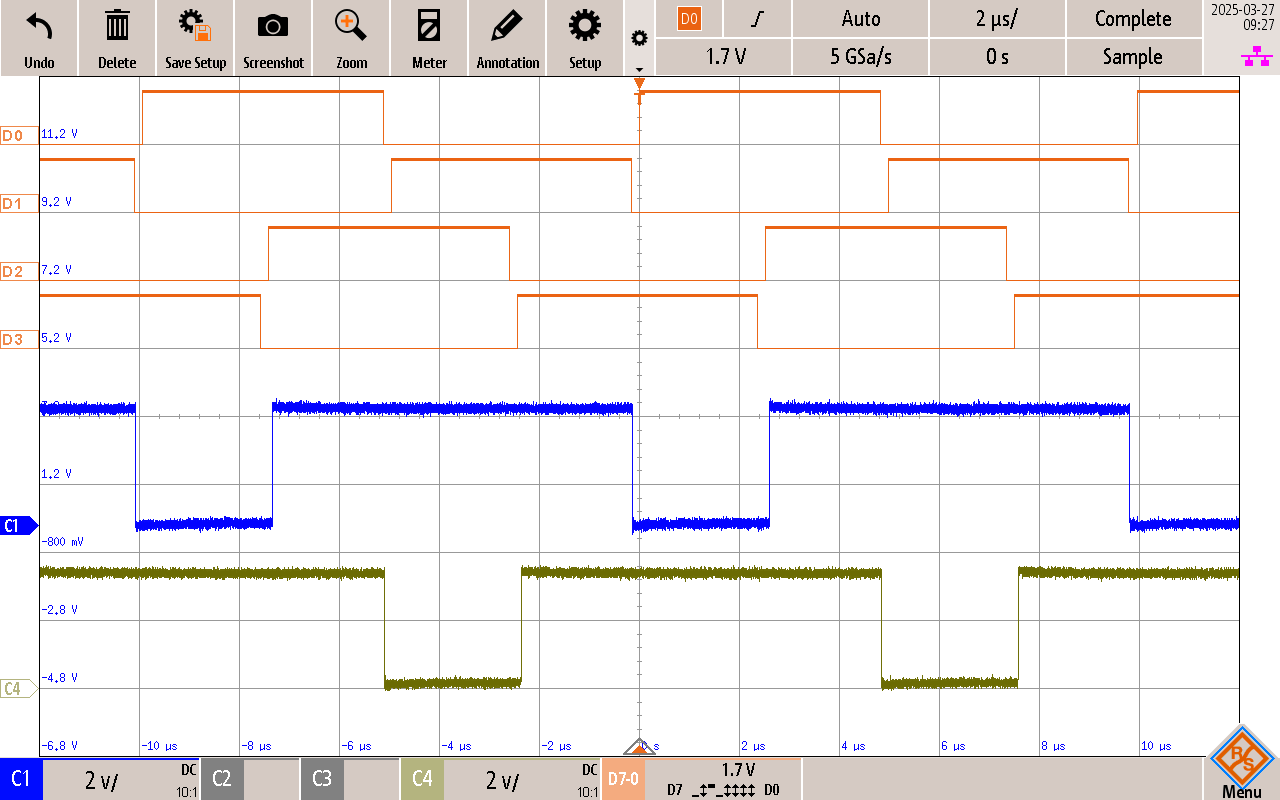

The control signal directed to the power stage is determined by the phase shift value between the fixed and phase-shifted legs. The primary side switches are actuated using the High-Resolution Pulse Width Modulation (PWM) with fine edge placement peripheral of the dsPIC33CK microcontroller. This peripheral is exceptionally versatile, facilitating the execution of intricate modulation schemes autonomously within the controller's core-independent peripheral. During phase-shifted operation, the phase-shifted leg is synchronized with the fixed leg. A phase shift is introduced to generate a bipolar voltage at the transformer, utilizing a highly adaptable trigger mechanism. This phase-shift is the control output from the compensator to the power stage. For more details on the workings of the PWM Peripheral, refer to the PWM Family Reference Manual. The Trigger mechanisms are summarized in the table below.

| PWM Generator Number | Details | Function | Start of Cycle Trigger | Peripheral Setting |

|---|---|---|---|---|

| PWM Generator 1 (PG1) | Complimentary PWM at 100kHz at 50% Duty Cycle, Dead Time 160ns | Generating Signals for the Fixed Leg of PSFB | Self-Running | PG1 End of Cycle |

| PWM Generator 3 (PG3) | Complimentary PWM at 100kHz at 50% Duty Cycle, Dead Time 160ns | Generating Signals for the Phase Shifted Leg of PSFB | Phase Delayed and Synchronized to PG1 | Trigger Value from PG1 |

| PWM Generator 2 (PG2) | Complimentary PWM at 100kHz, Swapped. Only High Side signal used | Generating the Synchronous rectifier signal for SR2 | Synchronized to PG3. Duty Cycle = Period – Phase Delay | Trigger value from PG3 and swapping the high and low side signal. |

| PWM Generator 4 (PG4) | Complimentary PWM at 100kHz, Swapped. Only High Side Signal used | Generating the Synchronous rectifier signal for SR1 | Synchronized to PG1. Duty Cycle = Period – Phase Delay | Trigger value from PG1 and swapping the high and low side signal. |

The PWM signals for the Secondary Rectifiers are generated using PWM Generator 2 (PG2) and PWM Generator 4 (PG4). The decision to turn on and off Secondary Rectifiers depends upon the load current. If the load current is high enough for CCM operation, then the Secondary rectifiers are turned on, otherwise the body diodes of the secondary side MOSFETs are used to conduct.

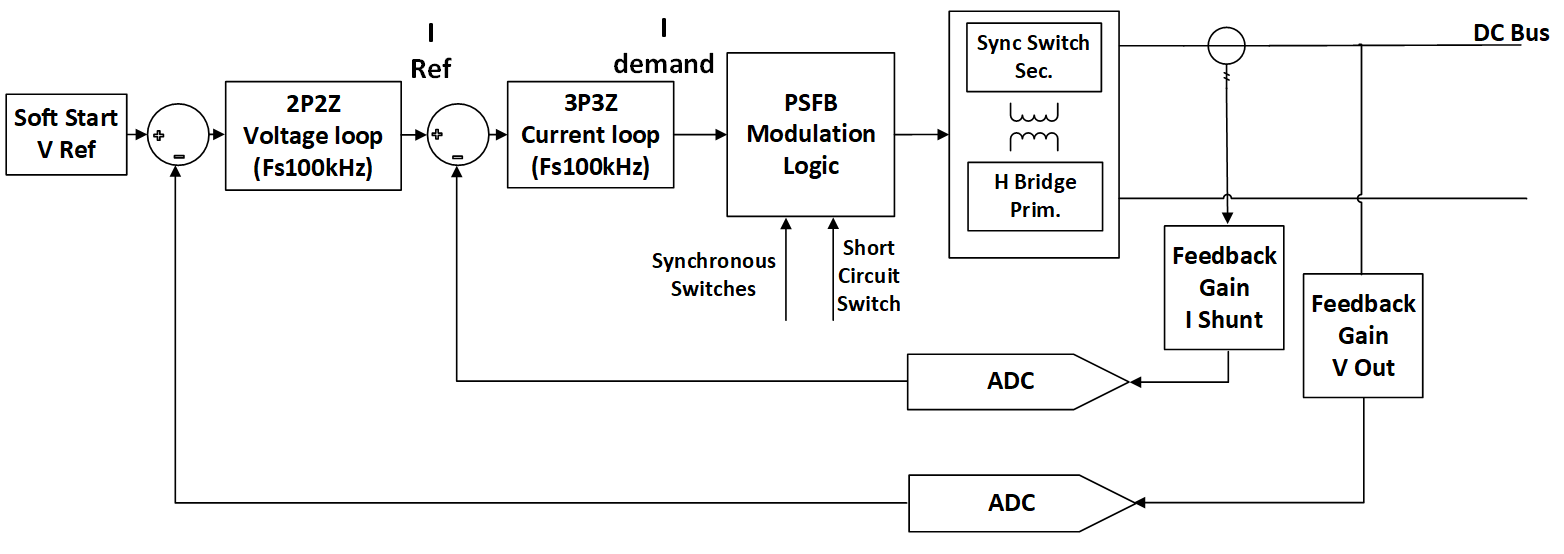

The changes to the input and output voltages and/or currents must not affect the stability of the system or damage the connected load. To ensure the integrity of the operation, the changes to the output and input voltages and currents are compensated for by using established control theory practices.

A fundamental approach to regulating the output voltage involves the implementation of a voltage loop. This voltage loop continuously monitors the output voltage for any deviations and compensates for these fluctuations by adjusting the controlled parameter applied to the plant (i.e. duty cycle, period, etc.) applied to the plant. However, relying solely on the voltage loop is often insufficient due to its inherently slow response time. Additionally, the voltage loop lacks the capability for cycle-by-cycle current control, which is critical for maintaining precise and stable operation. A cascaded approach is essential that employes both a current loop and a voltage loop.

To address the limitations inherent in the voltage loop, the inclusion of a current loop is essential. In the context of this design, two methodologies for current loops were evaluated: Peak Current Mode Control and Average Current Mode Control

In this design, the Average Current Mode is chosen. Average Current Mode Control provides various advantages in the context of Power Converter methodology, such as easier control schemes, working better with droop control methods, and providing more flexibility for maximum efficiency as it gives more control over edge positions.

Peak Current Mode Control (PCMC) has its own advantages, such as rapid transient response and reduced computational workload on the CPU.

The fundamental difference between PCMC and Average Current Mode Control (ACMC) lies in managing transformer magnetization and current regulations.

PCMC aims to prevent staircase saturation by ensuring equal currents, whereas ACMC achieves this by enforcing equal on-times to maintain balanced magnetization in the transformer. PCMC requires a highly symmetric current sense signal. On the contrary, ACMC is more tolerant of imprecise feedback, if the half-bridges respond uniformly.

In well-designed systems, the switch timings of each bridge are typically synchronized, making ACMC a straightforward approach due to its leniency towards feedback signal symmetry. This tolerance simplifies the design process, as achieving a perfectly symmetric current feedback signal is not always feasible.

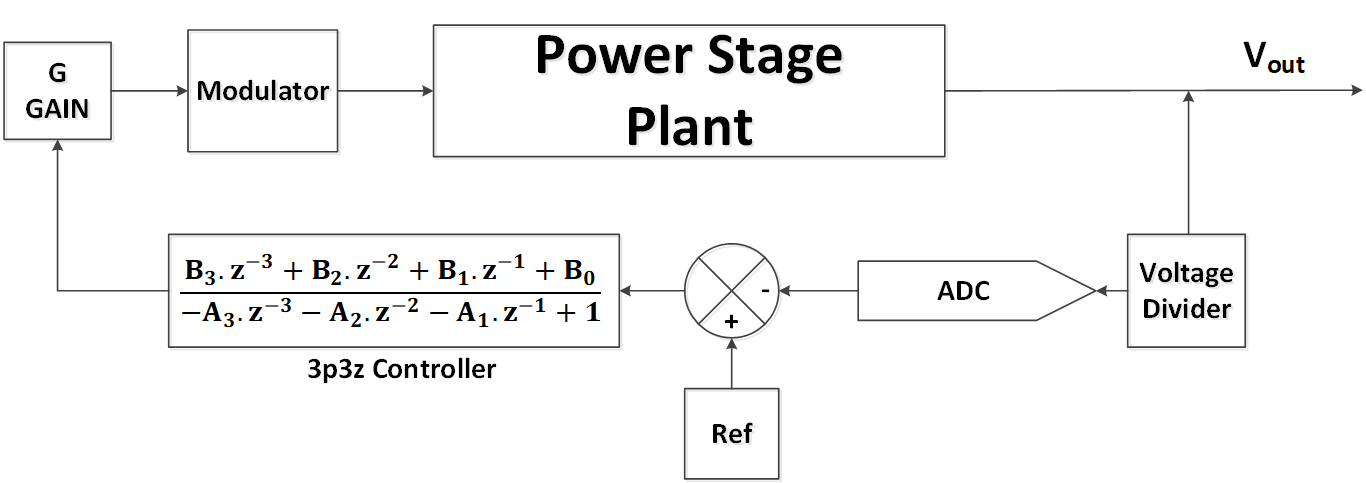

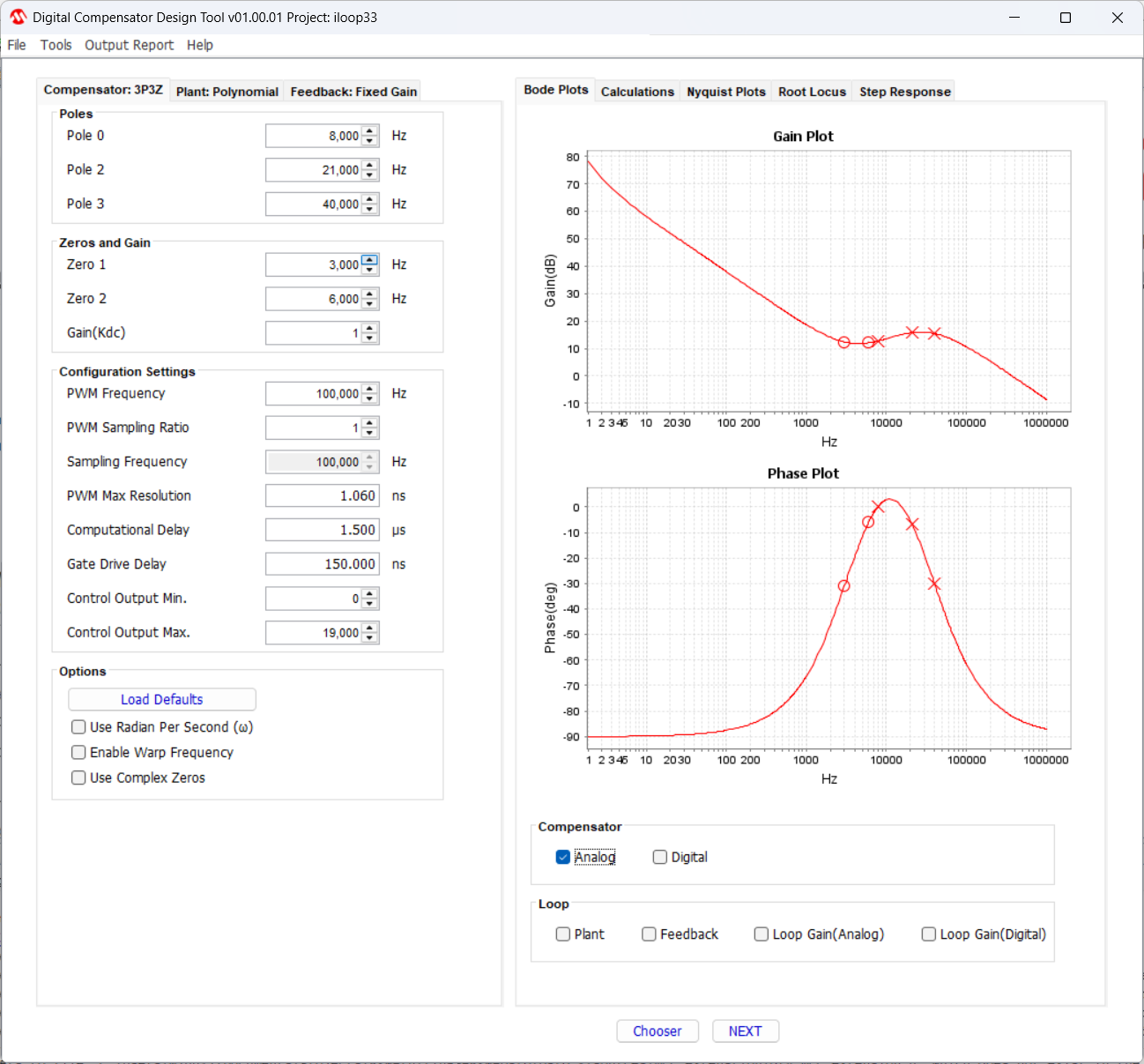

The 2-pole/2-zero and 3-pole/3-zero are digital implementations of type II analog and type III analog compensators. These are filters designed to introduce specific gain and phase boosts by strategically placing poles and zeros in the frequency domain.

For Current loop a 3 pole 3 zero compensator is used, and for Voltage Loop a 2 Pole 2 zero compensator is used. These values gave enough margin in the overall system response for gain and phase to ensure a stable operation. For test results please refer to the operational manual.

| 3p3z Current Loop | Frequency(Hz) |

|---|---|

| Pole 0 | 8000 Hz |

| Pole 2 | 21000 Hz |

| Pole 3 | 40000 Hz |

| Zero 1 | 3000 Hz |

| Zero 2 | 6000 Hz |

| 2p2z Voltage Loop | Frequency(Hz) |

|---|---|

| Pole 0 | 60 Hz |

| Pole 2 | 45000 Hz |

| Zero 1 | 40 Hz |

The Analog controllers of two poles two zeros, and three poles three zeros are implemented in the digital domain by transforming the compensator transfer function from the s-domain to the z-domain.

The Digital Compensator Design Tool (DCDT), a complimentary plugin available within the MPLAB X Integrated Development Environment (IDE), is employed to determine the digital compensator coefficients by entering the location of Poles and Zeros in frequence domain. Based on the locations of the poles and zeros, the coefficients for the z-domain equation are computed.

These coefficients are utilized within the Switched-Mode Power Supply (SMPS) control library, which is also provided free of charge by Microchip. The SMPS control library offers efficient and high-speed assembly libraries to facilitate the updating of control loops. For more information on DCDT refer to the DCDT’s webapage.

The diagram illustrates the comprehensive control scheme for the PSFB DCDC converter. The outer voltage loop acquires its reference through a soft-start mechanism, wherein the reference is incrementally ramped up. This outer voltage loop subsequently provides a reference to the internal current loop. Both control loops operate on a cycle-by-cycle basis.

There are two levels of Fault monitoring and handling.

The primary over current Fault handling is done by monitoring the input current using a comparator.

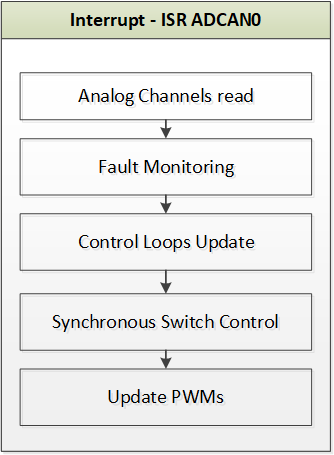

dsPIC33CK has high speed analog comparator with slope compensation DAC. The Primary Overcurrent condition will trigger a fault, which will stop switching on the primary side. The secondary rectifiers will be turned off as soon as the current falls below a certain threshold.

The Primary Over/Under Voltage, Secondary Over/Under voltage, Secondary Overcurrent, and Over Temperature are sensed through ADC and monitored for fault conditions every PWM cycle of the fixed leg. The fault response is the same as the hardware fault response, i.e. turn off the PWM signals for fixed and phase shifted legs. Secondary side switches are turned off when the current falls below CCM/DCM threshold.

The PSFB has an isolated CAN-FD interface. The design is intended to work with Power Board Visualizer. With Power Board Visualizer the important parameters and the current state of the PSFB can be observed in real time. The output voltage reference can also be changed using a voltage slider.

dsPIC33CK comes with a highly versatile CAN FD module. The transmission and receiving of messages are taken care of by the peripheral.

The complete information about the CAN-FD messages can be seen by clicking the info tab of the PBV Project.

The system monitors additionally the five-volt line, as well as the system temperature. Overtemperature, or a dip in five-volt line will also generate a fault condition.

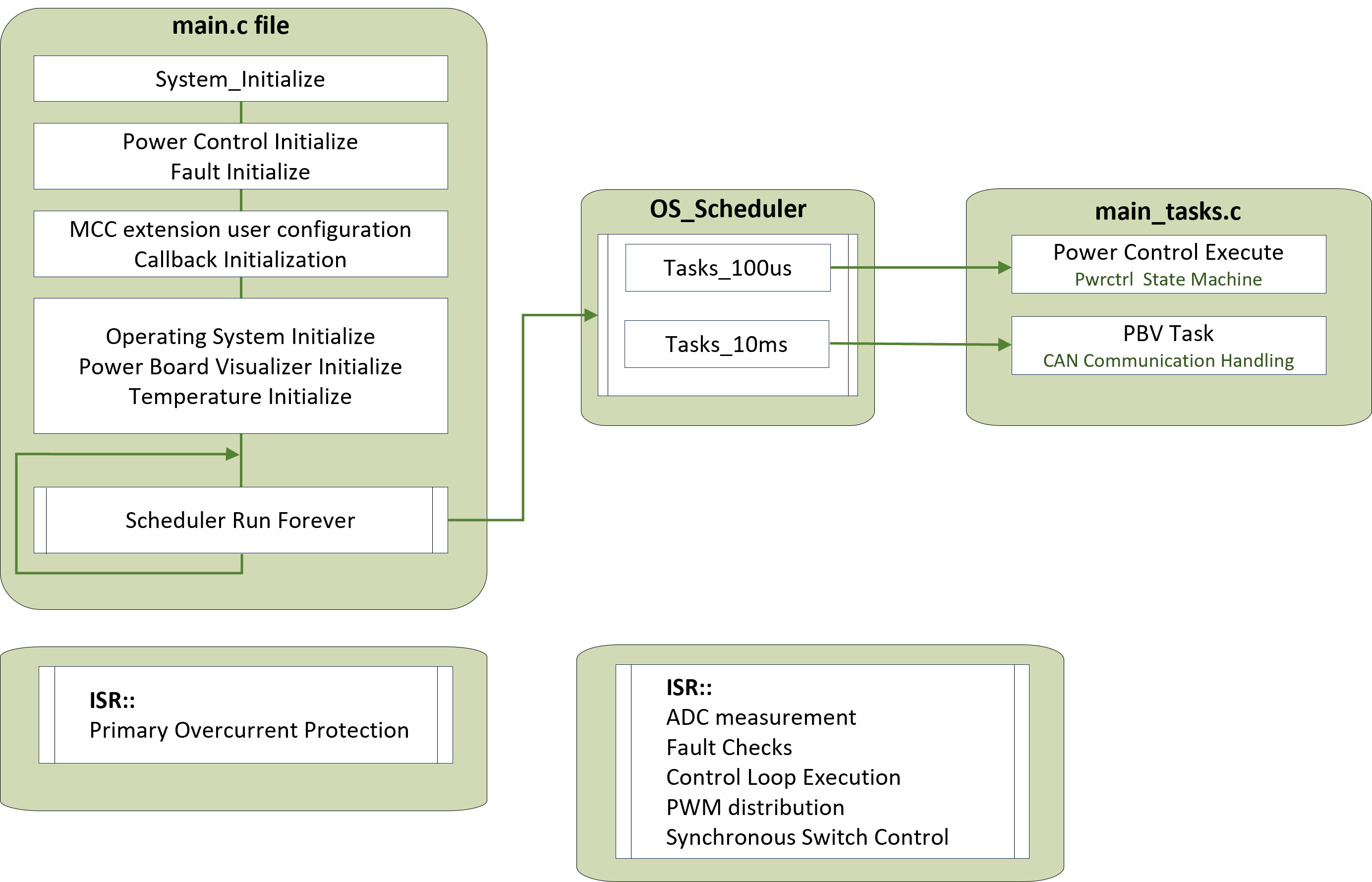

The firmware architecture uses a simple yet effective task scheduler. This simple task scheduler enables different tasks to run at different frequencies. The system tick is generated by using the Timer 1 of the dsPIC33CK.

The state machine of the Power supply is updated every 100us using the 100us task update of the scheduler.

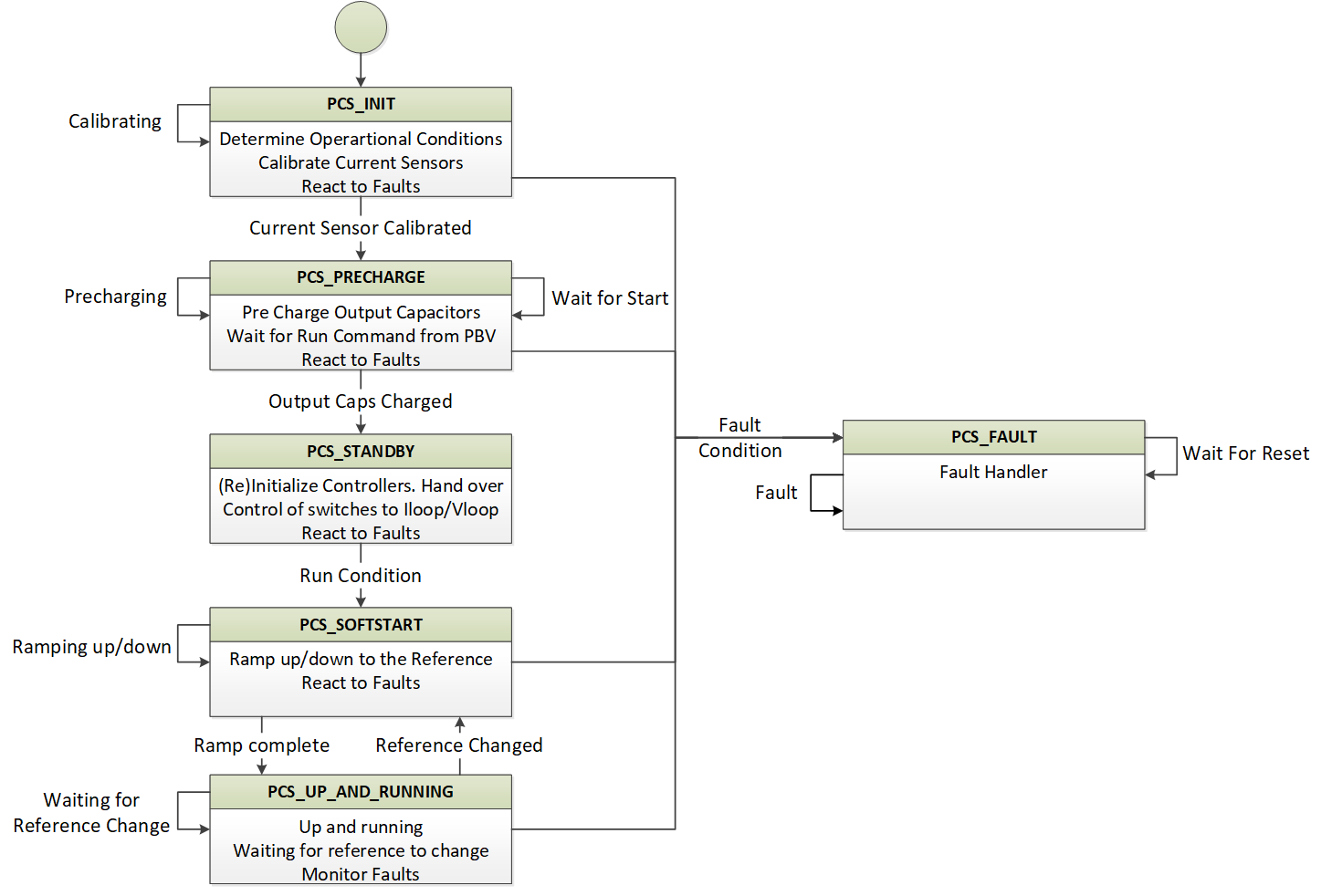

Initial State of the power converter. In this state the sensor offsets are measured, and the system transtions for PCS_PRECHARGE State

Next State of the power converter. here the converter waits for the Start Precharge command from PBV. After the Precharge, it stays in this state, and waits for the Start Power Transfer command from the PBV.

In this state all the controllers are Initialized. And then the control of the switches is handed over to Control loops, and the SR control is handed over to DCM/CCM monitor

In this state, the Voltage reference to the loop is ramped up and down.

In this state, the controller maintains the output voltage to the setpoint from Power Board Visualizer. In case the user changes the voltage reference from PBV using the voltage reference slider, the refernce is incremently/decremently applied to the voltage loop in the PCS_SOFTSTART state.

In any fault condition, the primary side switches are turned off. The output current is allowed to dissipate, and then the Secondary Rectifiers are turned off. The system is taken out of Fault condition by clicking the Fault Reset button on PBV. Note that if the conditions for fault exist, then the system will immediately jump back into fault state.

In parallel to Statemachine, an interrupt is generated synchronized with the fixed leg PWM signal. Here all the analog values are updated. These are triggerd as described above. Based on these values faults are monitored, and control loop's feedbacks are updated, and new control loops output values are used to update the PWM Duty Cycles.

The secondary side current read here is also responisble to determine the CCM/DCM conditions. The Secondary Rectifiers are switched on and off based on the output current.

Microchip Code Configurator (MCC) is a user-friendly software tool designed to simplify the development process for embedded applications. It offers a graphical interface that allows developers to easily configure and generate initialization and application code for Microchip's 8-bit, 16-bit, and 32-bit microcontrollers. By automating the setup of peripherals and libraries, MCC enables developers to concentrate on creating their application logic, reducing development time and effort. MCC is used to configure all the peripherals of the dsPIC33CK for this project.

MCC comes bundled together with MPLAB X Ide. To visualize the periphreal settings for this projects please click on MCC icon from the toolbar of MPLAB X Ide, once the project has been opened.

© 2025, Microchip Technology Inc.