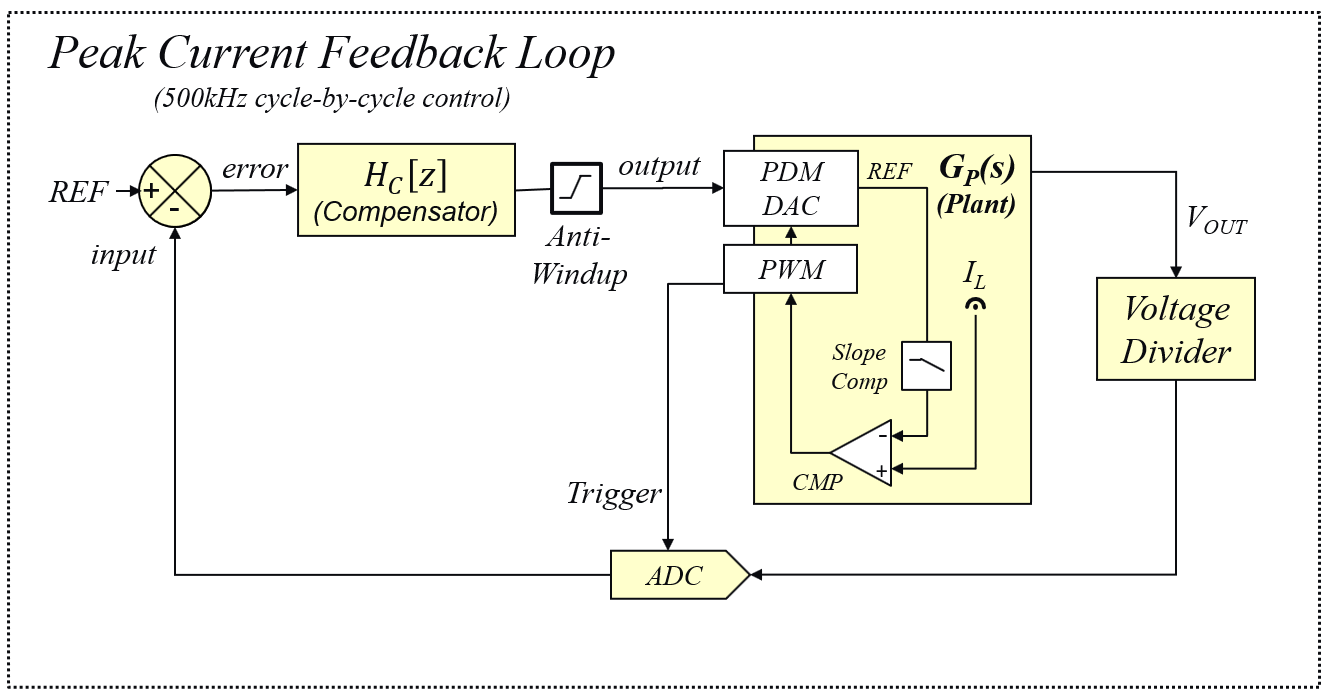

This firmware demonstrates the implementation of a simple, single loop peak current mode controller used to regulate the constant output voltage of the on-board step-down converter of the Digital Power Starter Kit 3 (DPSK3). The implementation of the Voltage Feedback Loop requires one Analog-to-Digital Converter (ADC) input oversampling the output voltage of the converter and two PWM outputs (PWM high and PWM low) to drive the power converter half-bridge switch node in synchronous mode. The current feedback is generated by a current sense transformer, providing the positive slope of the triangular inductor current to an analog on-chip comparator. If the current feedback signal exceeds the internally applied reference signal, the comparator trips the PWM logic, truncating the active on-time.

[back]

Figure 1 shows the block diagram of the buck converter peak current mode controller, where the ADC input is used to sample the most recent level of the output voltage feedback signal. Once converted, the value is then compared against the internal reference value and the inverse of the deviation between reference and feedback (= error) is pushed through the discrete compensation filter.

In the Anti-Windup block, the output of the compensation filter is checked against user-specified minimum and maximum thresholds. Should any of these thresholds be exceeded, the controller output will be overwritten with the respective threshold value before being written directly to the Digital-to-Analog Converter (DAC) register applying the reference to the internal comparator. The comparator output is triggering the PWM logic when the inductor current feedback exceeds teh reference, which will terminate the active on-time (output PWMxH going low).

Light load operation of the controller implementation used in this code example observes the most recent control output written to the DAC providing the reference voltage to the switch-node comparator. This reference level represents the desired peak current of the inductor current and therefore relates to the power output of the converter. Below a certain threshold, the switching losses created by operating the low-side rectifier FET exceed the power loss savings gained by operating a FET instead of a passive rectifier diode. Below this power level the low-side FET is therefore turned off using its body diode to rectify the current, effectively switching the synchronous buck converter into asynchronous operation.

As a result, the duty ratio may drop to zero until the converter ends up in burst mode operation under no-load conditions, where a sequence of short pulses is generated to recharge the output capacitor. As soon as the control loop produces a DAC value grater than the user-defined threshold, the converter will switch back into synchronous operation for improved efficiency in continuous conduction mode.

[back]

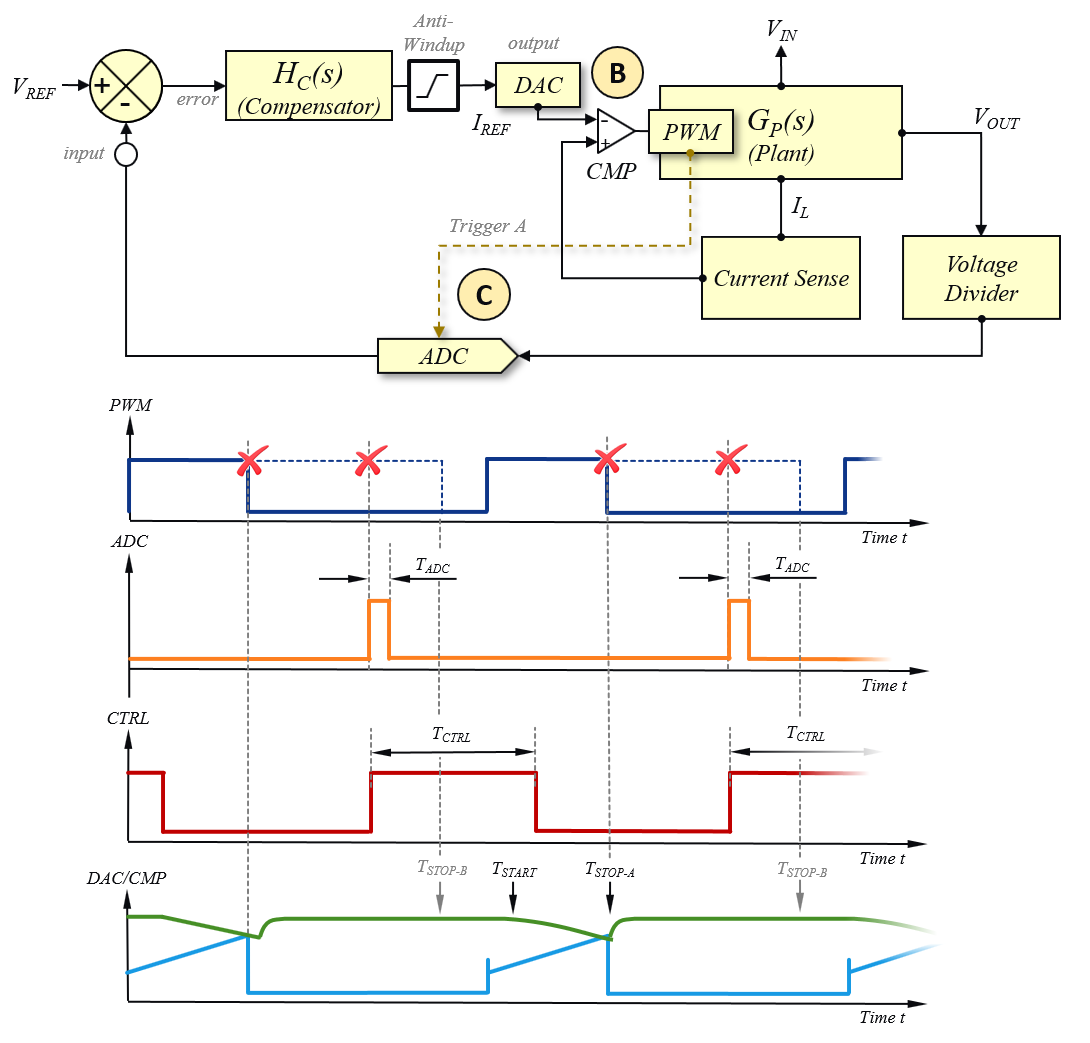

The single, outer voltage loop controller is triggered by the PWM counter at the same time as the ADC is triggered. The control loop is executing the overhead code of calculating the first part of the compensation filter term (= A-Term) until the most recent ADC sample is available to be processed in the later part of the compensation filter term computation (= B-Term). This approach helps to shorten the overall response time of the controller measured between ADC trigger and write back event of the most recent controller result to the DAC register. The ADC trigger point is positioned towards the end of the period leaving enough room for the computation to complete before the next cycle end is expected. By placing the ADC trigger point as late as feasible within the period, the total control response time is less than half a switching period, resulting in minimized phase erosion.

[back]

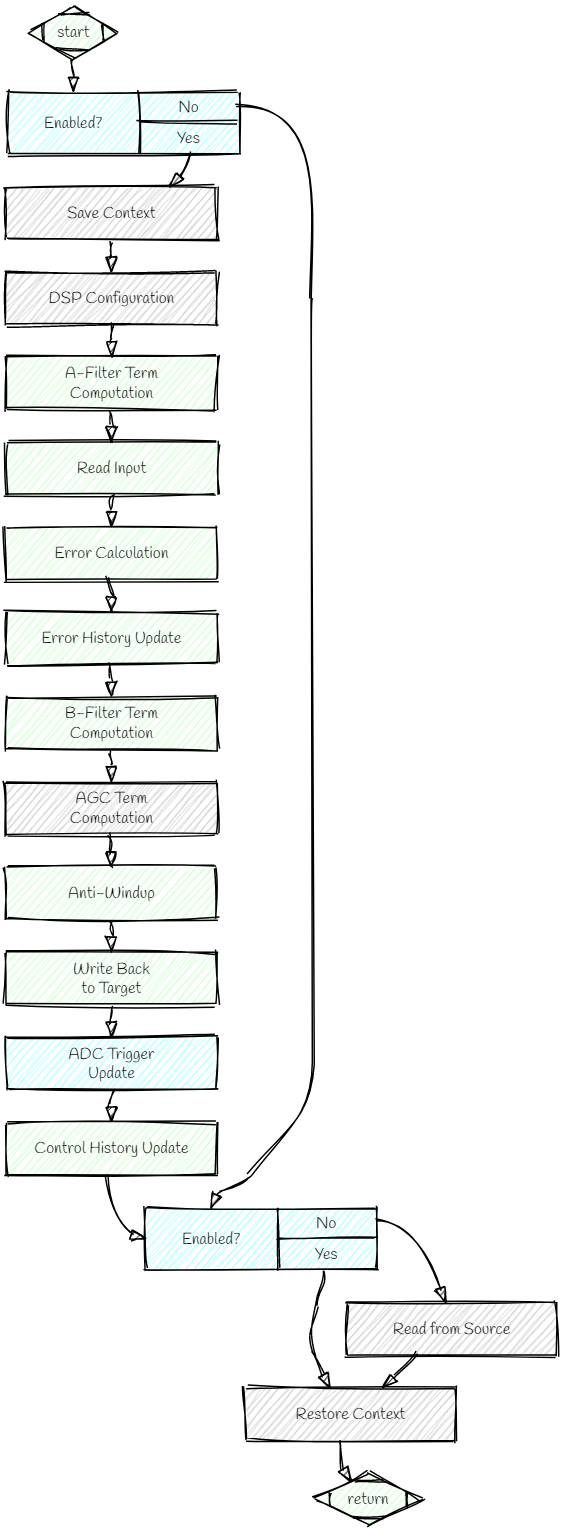

Figure 3 shows a typical flow chart of a discrete software feedback loop called at the desired control frequency. It covers the loop path from ADC trigger to DAC update shown in the block diagram above (see Figure 2) while supporting additional features like an Enable/Disable Bypass Switch.

[back]

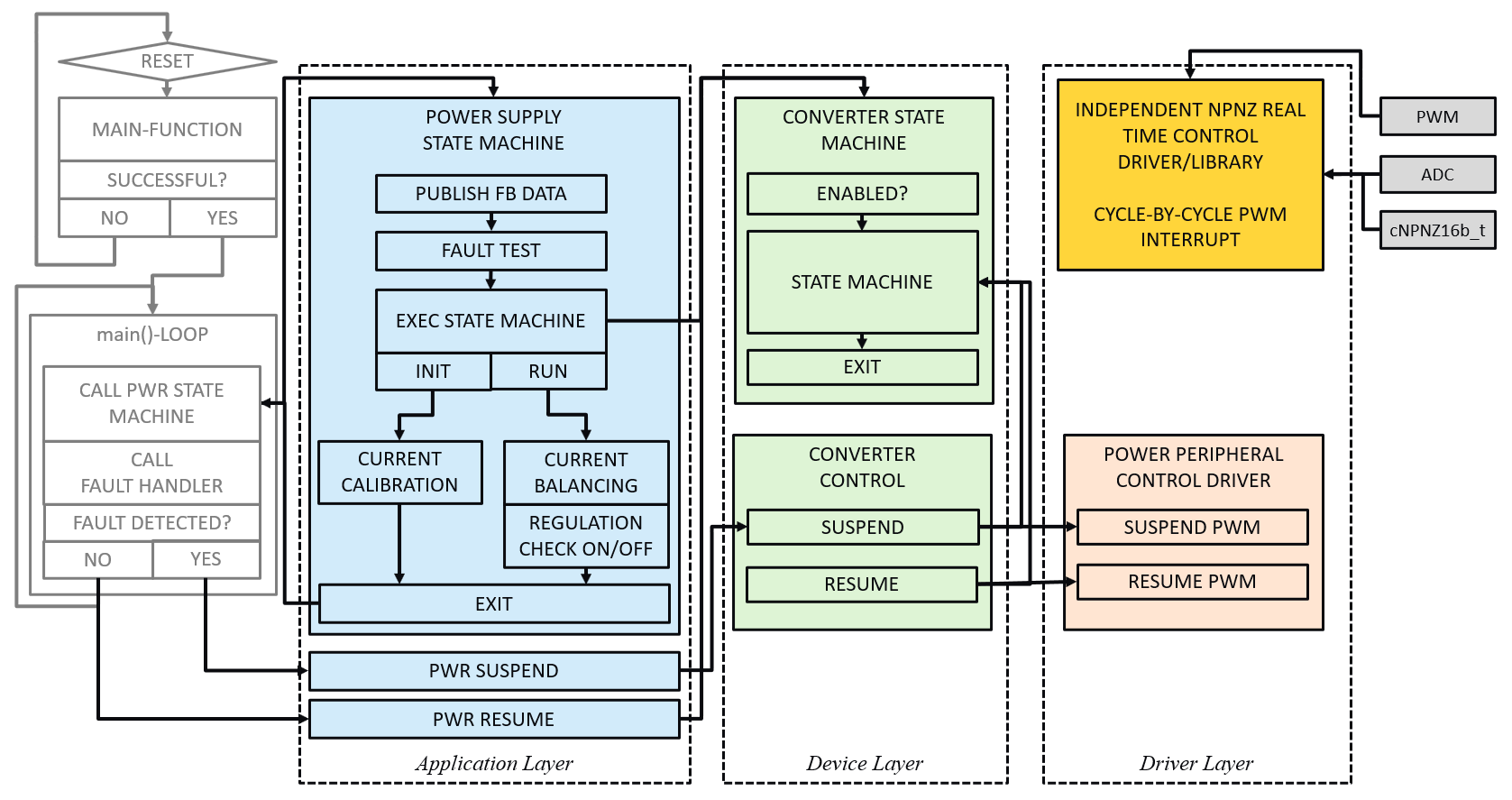

Figure 4 shows a typical implementation of the power converter state machine and the high-speed control loop in a task scheduler based firmware environment.

More detailed information on the library implementation, such as task and library APIs, can be found in the chapter Software Overview on the left side of this window.

[back]

(c) 2021, Microchip Technology Inc.